The Effects of Poly Corner Etch Residue on Advanced FinFET Device Performance

June 16, 2021

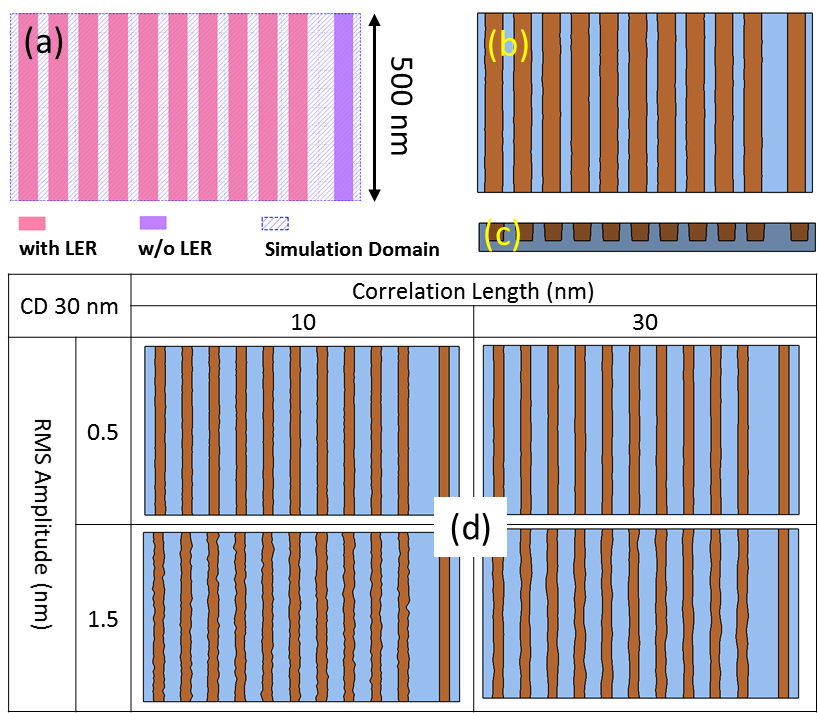

A Study of the Impact of Line Edge Roughness on Metal Line Resistance using Virtual Fabrication

August 18, 2022You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. If you do not have an account, we invite you to request an account.

Whitepaper: Evaluating the Impact of STI Recess Profile Control on Advanced FinFET Device Performance

To download your free white paper, please fill out the form below:

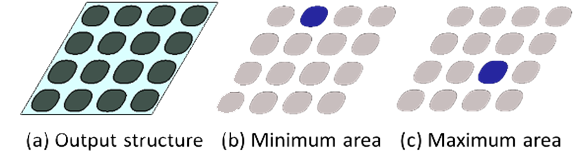

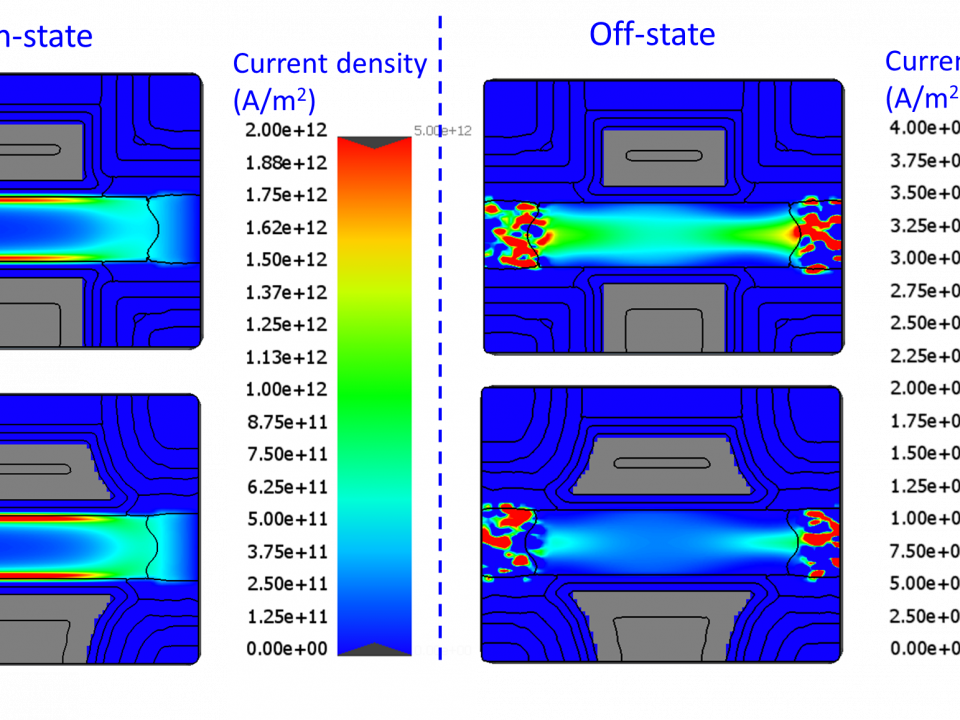

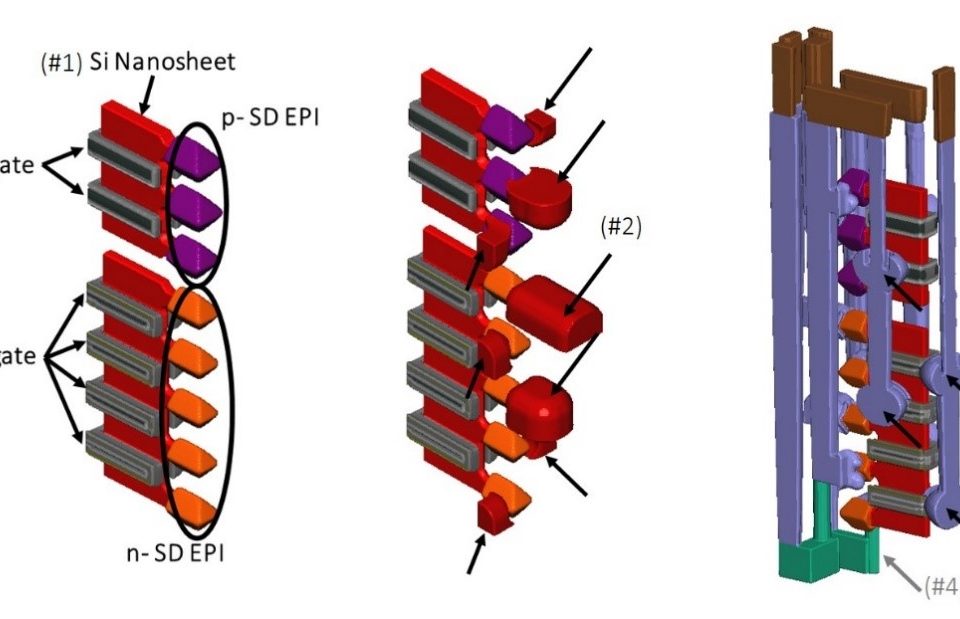

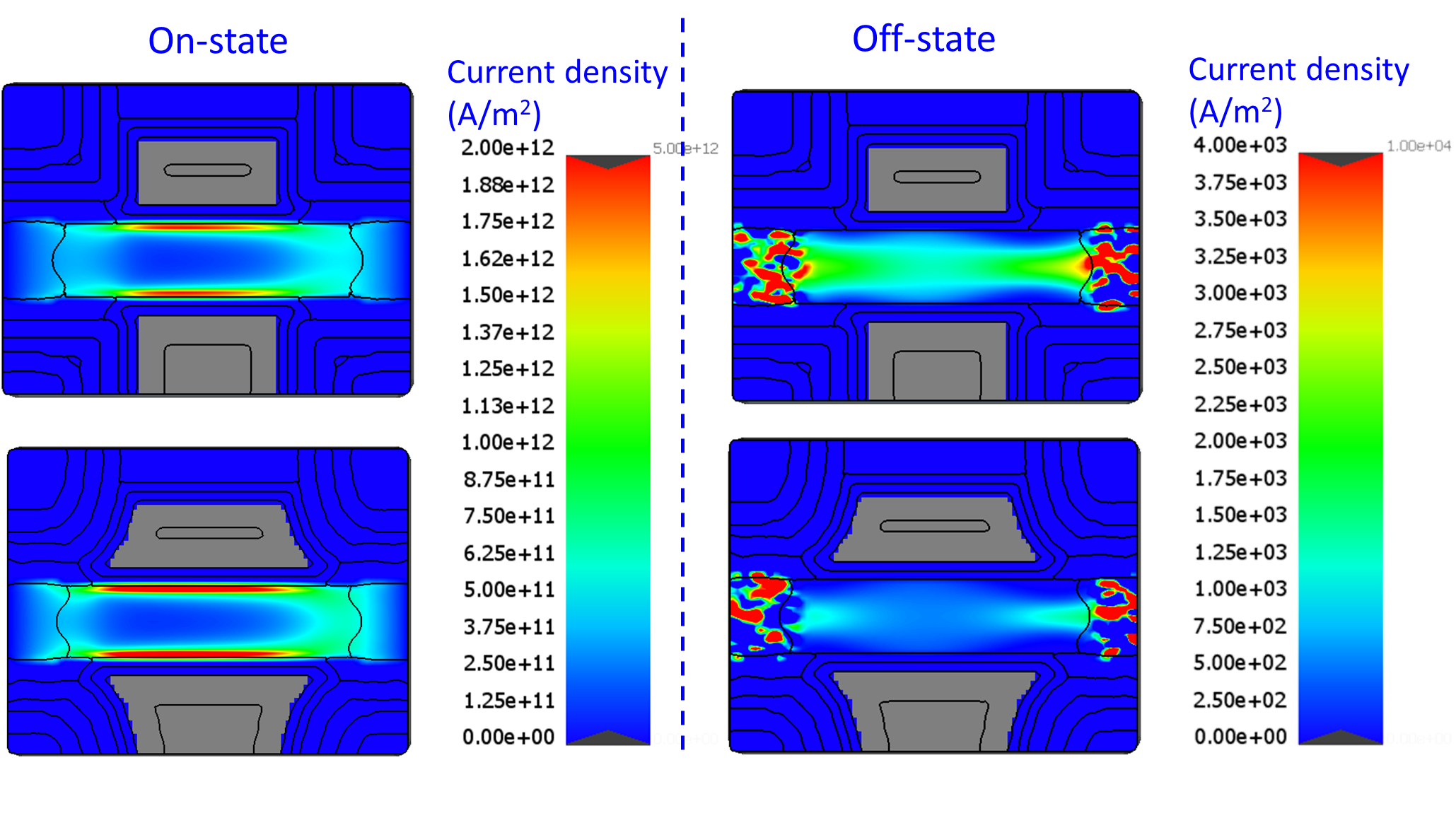

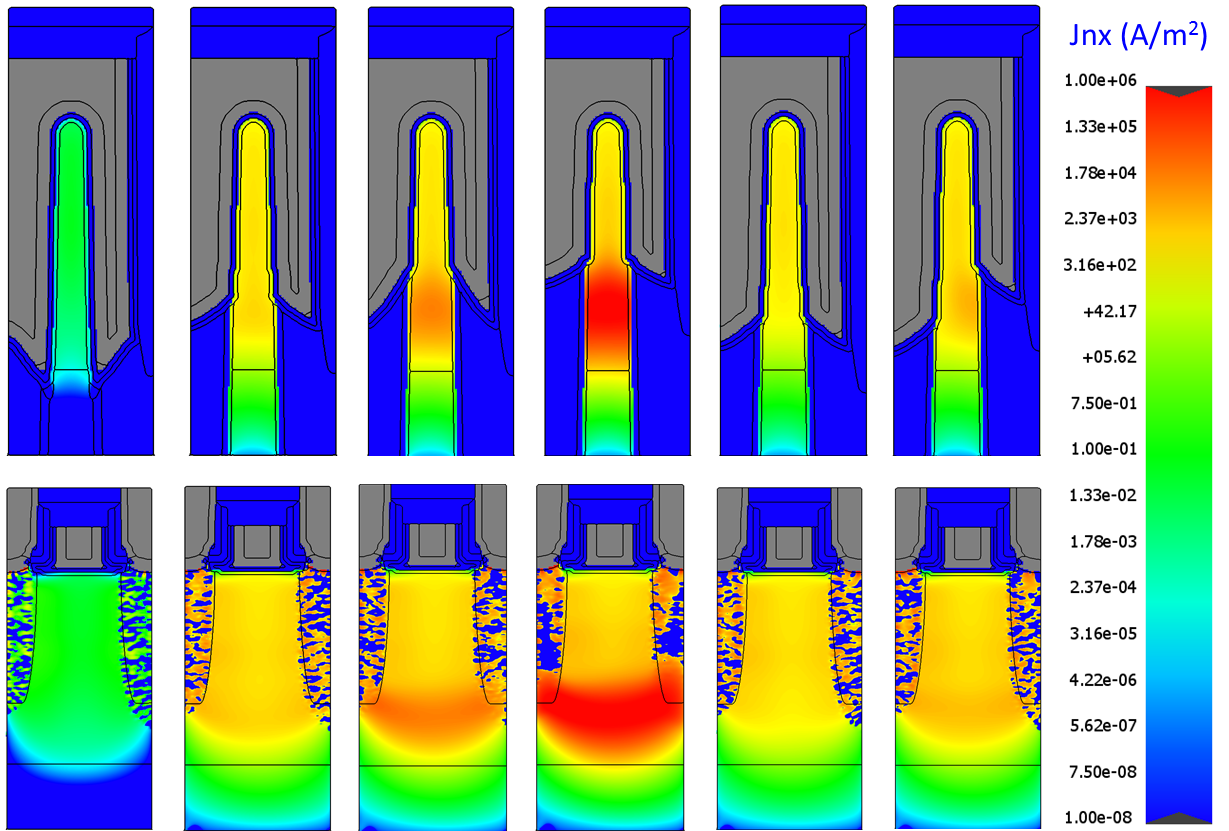

In this paper, a 5nm FinFET flow was built using the SEMulator3D® virtual fabrication platform. Different STI (shallow trench isolation) recess profiles were investigated using the pattern-dependent etch capabilities of SEMulator3D, including changes in trenching/footing profile, fin height and imbalance fin height. The impact of STI recess profile on device performance was then investigated using a built-in drift-diffusion solver. Our analysis has confirmed that larger footings, lower fin heights and larger imbalance fin heights will generate more severe DIBL problems and lead to higher off-state leakage. STI recess with an optimal trenching profile can increase on-state current and reduce off-state leakage.

You might also be interested in:

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]