You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. If you do not have an account, we invite you to request an account.

Whitepaper: Pathfinding by process window modeling: Advanced DRAM capacitor patterning process window evaluation using virtual fabrication

To download your free white paper, please fill out the form below:

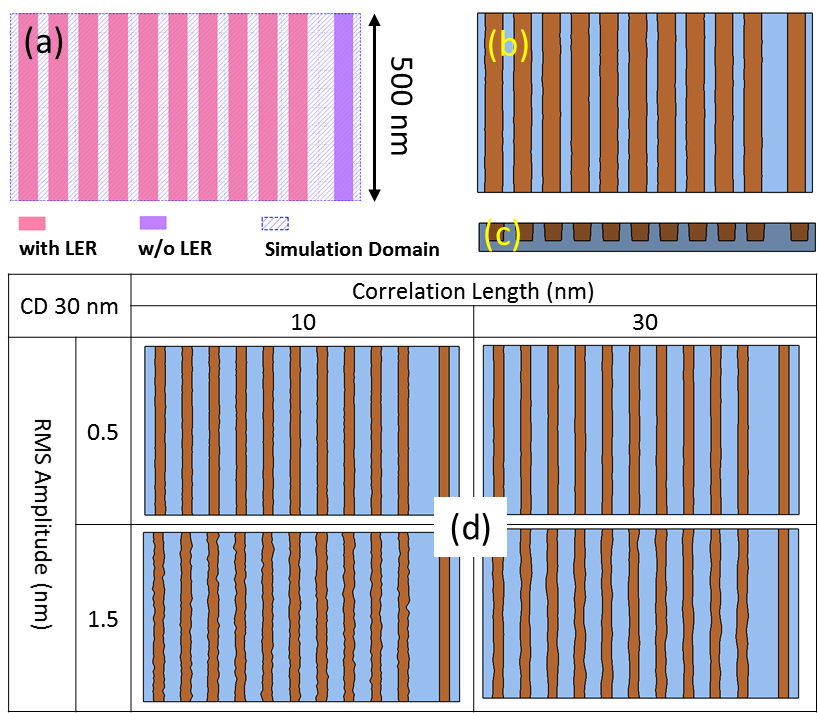

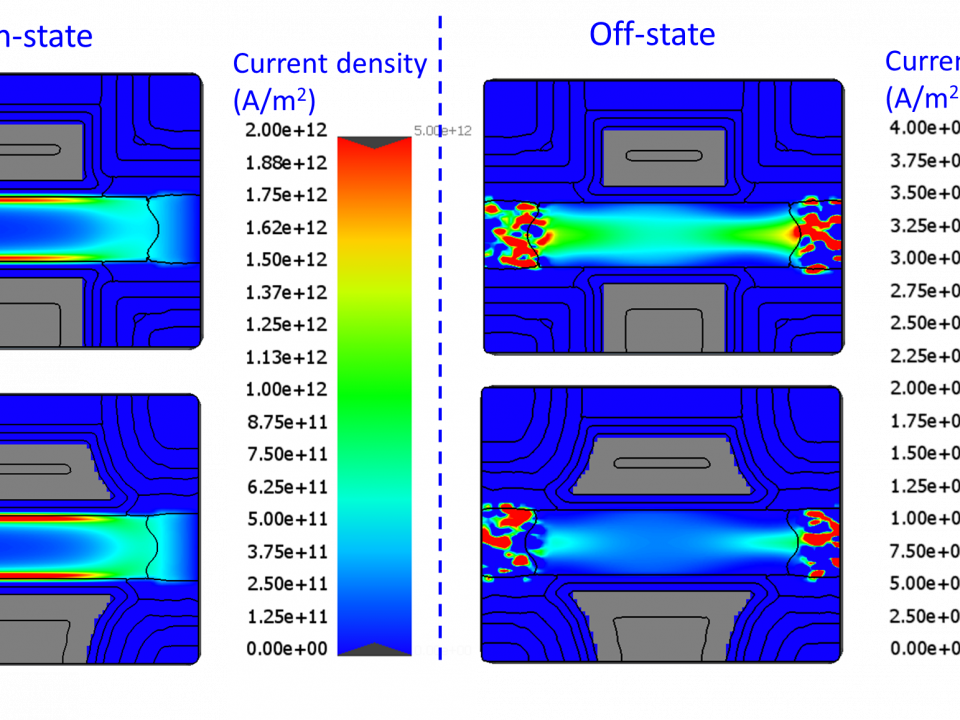

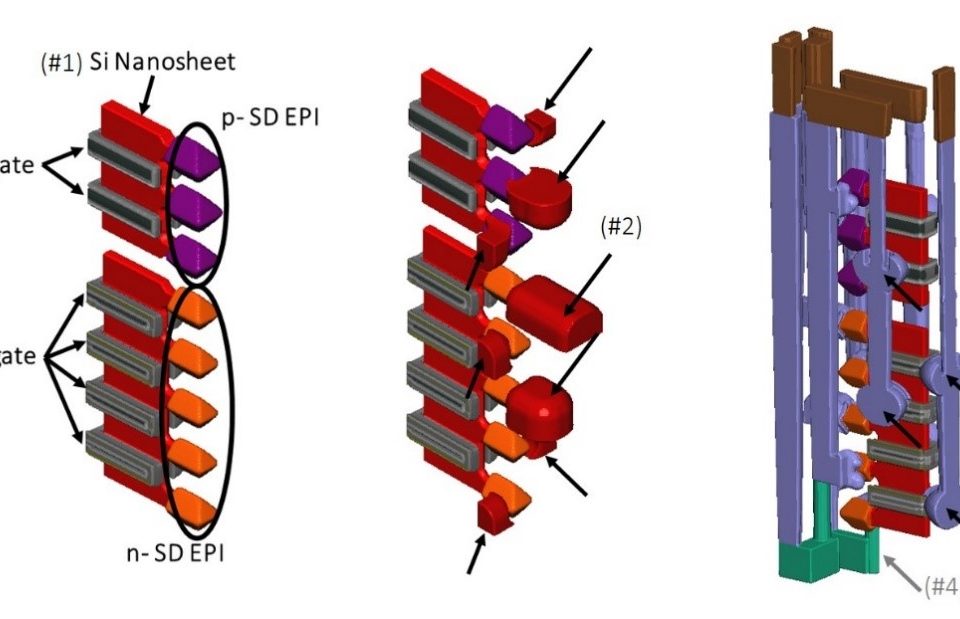

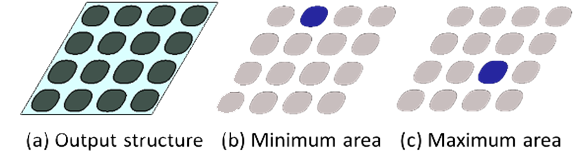

In advanced DRAM, capacitors with closely packed patterning are designed to increase cell density. Thus, advanced patterning schemes, such as multiple litho-etch, SADP and SAQP processes may be needed. In this paper, we systematically evaluate a DRAM capacitor hole formation process that includes SADP and SAQP patterning, using virtual fabrication and statistical analysis in SEMulator3D®. The purpose of this analysis is to obtain a quantified process window comparison between the SADP and SAQP patterning schemes.

© 2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

You might also be interested in:

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]