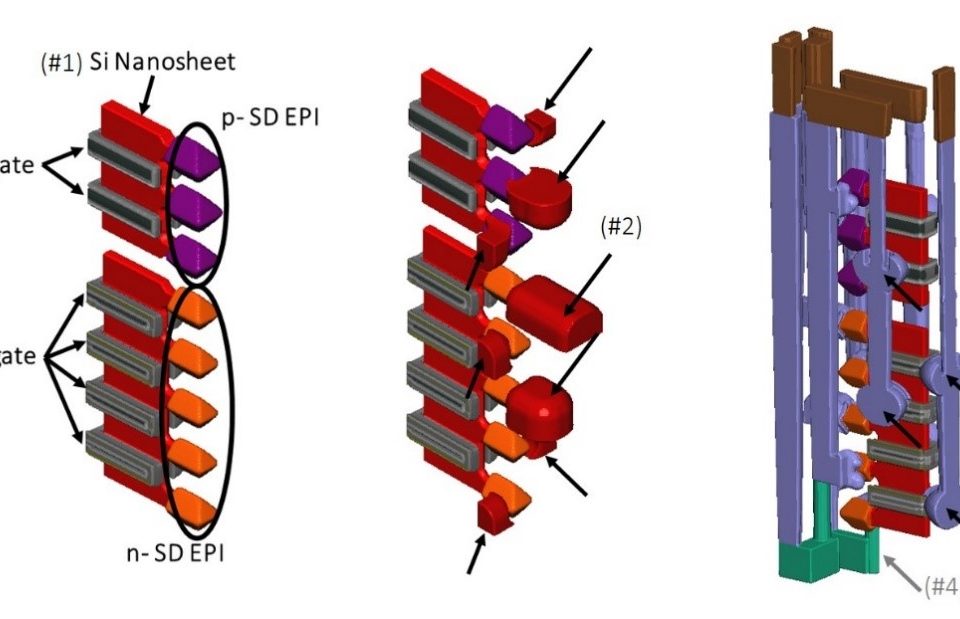

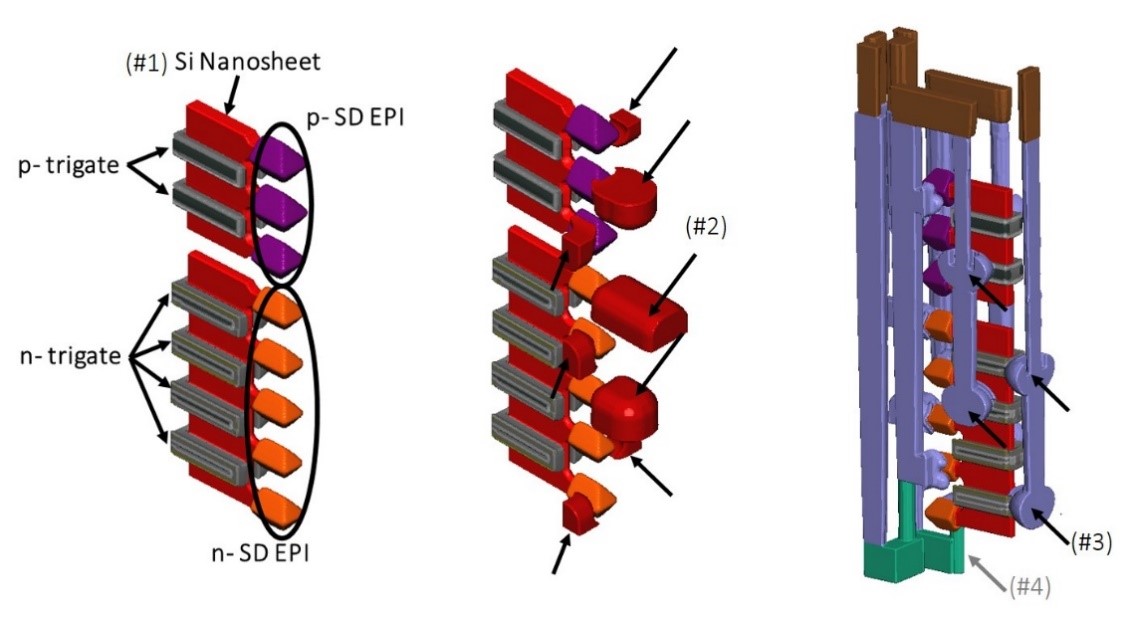

SVT (six stacked vertical transistors) SRAM cell architecture introduction: design and process challenges assessment

March 8, 2021

Evaluating the Impact of STI Recess Profile Control on Advanced FinFET Device Performance

September 14, 2021You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. If you do not have an account, we invite you to request an account.

Whitepaper: The Effects of Poly Corner Etch Residue on Advanced FinFET Device Performance

To download your free white paper, please fill out the form below:

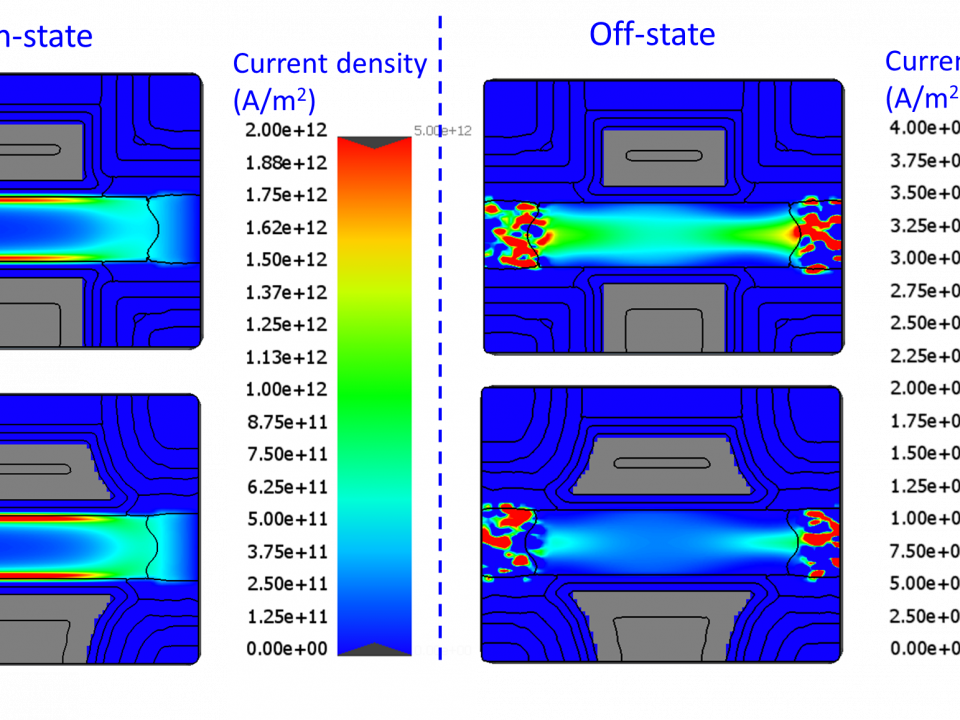

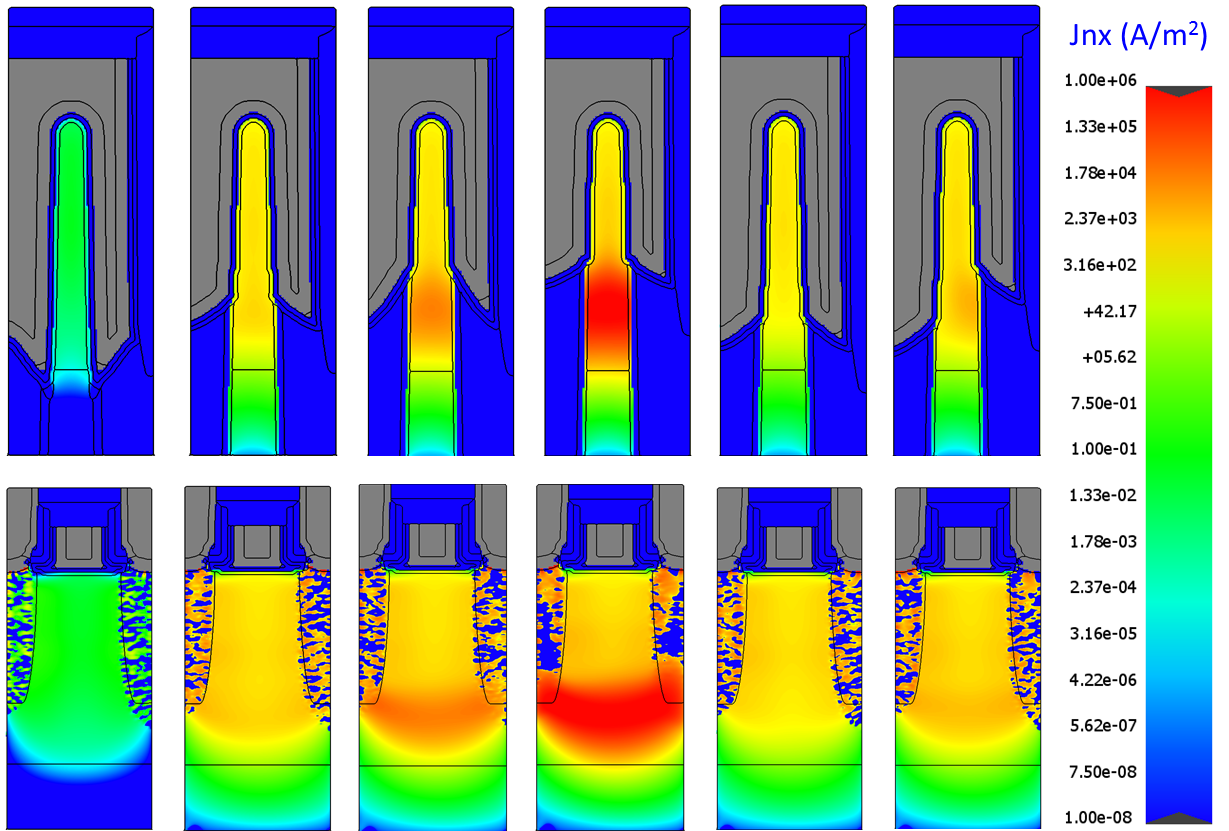

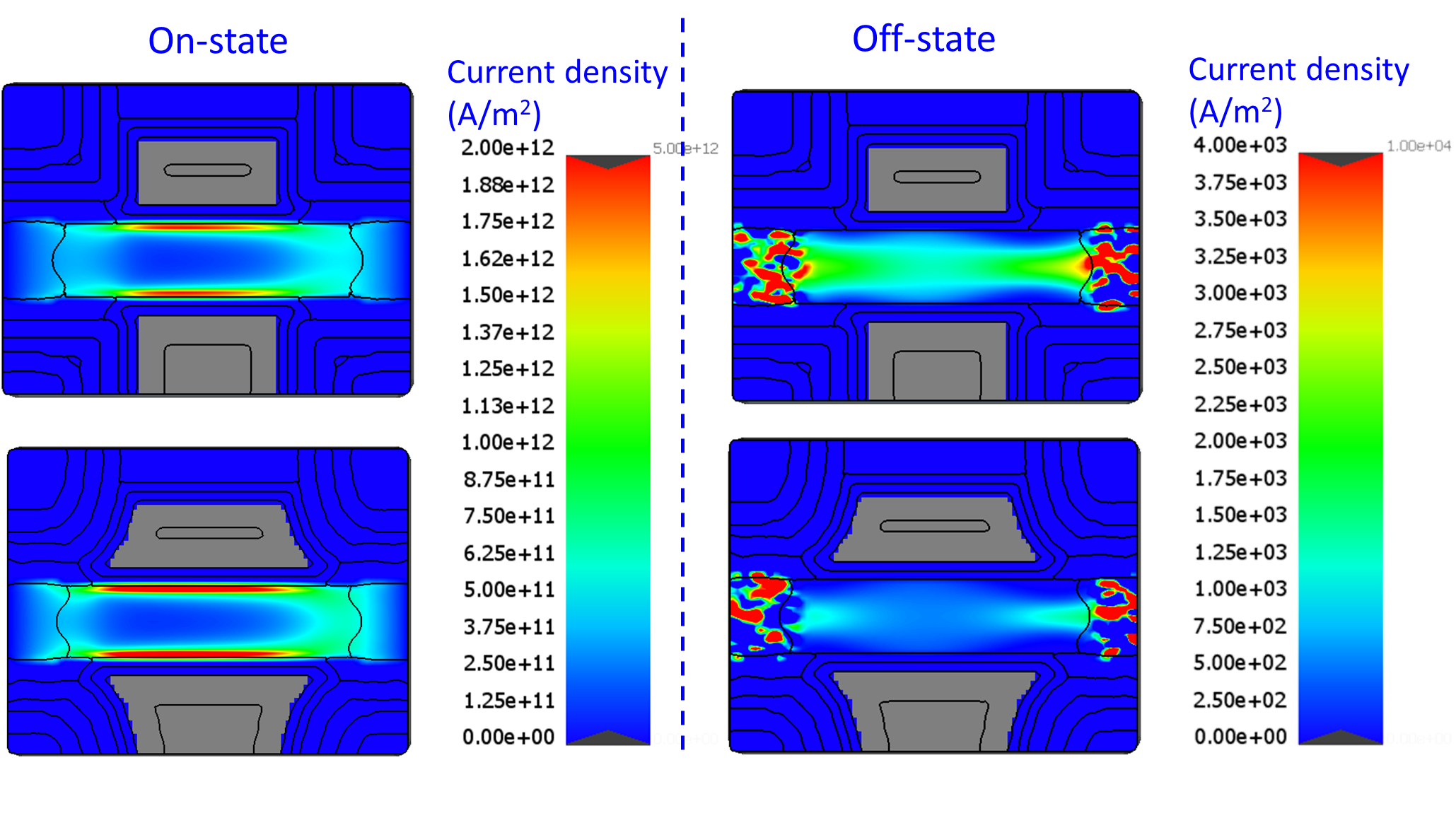

In this paper, we study the effect of poly corner residue during a 5nm FinFET poly etch process using virtual fabrication. A systemic investigation was performed to understand the impact of poly corner residue on hard failure modes and device performance. Our results indicate that larger width and height residues can lead to a hard failure by creating a short between the source/drain epitaxy and the metal gate. Surprisingly, a properly-sized residue can boost device performance with a greater than 8% on-state current increase and about a 50% off-state current drop, compared with having no poly corner residue. This increase in performance is primarily due to the reduction of access resistance between the source/drain and gate during the on-state, and better gate control during the off-state. This study demonstrates that proper residue size and variation control in the poly etch process is required to balance yield and device performance.

You might also be interested in:

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]