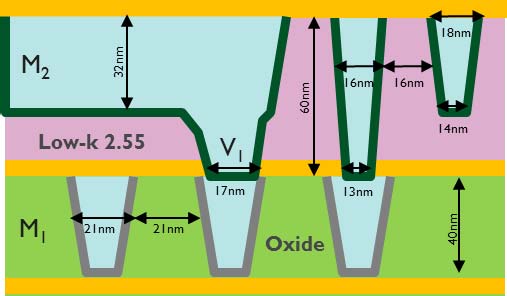

Modeling of Tone Inversion Process Flow for N5 Interconnect to Characterize Block Tip to Tip

September 21, 2017

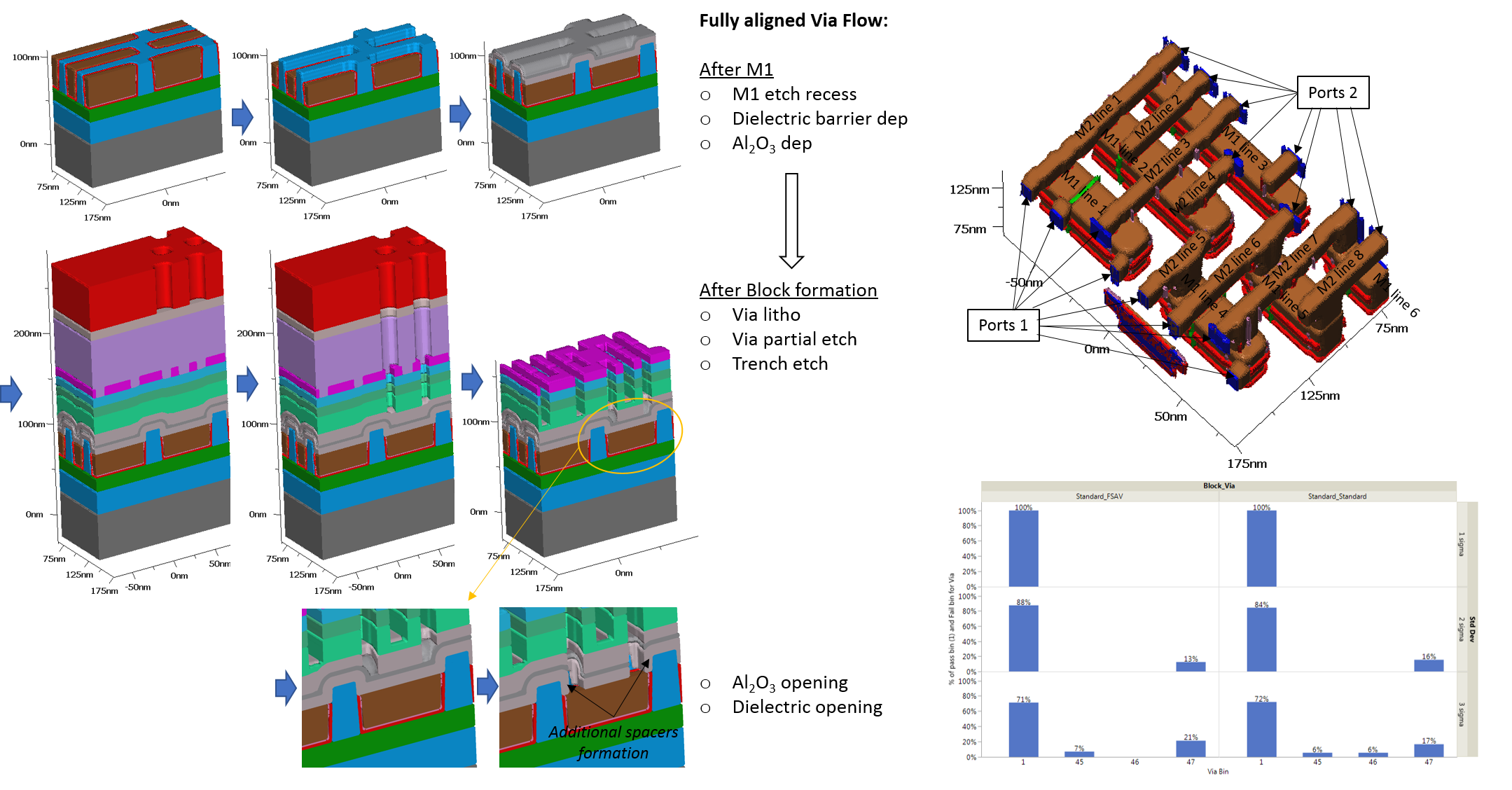

Self-Aligned Block and Fully Self-Aligned Via for iN5 Metal 2 Self-Aligned Quadruple Patterning

March 14, 2018You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. If you do not have an account, we invite you to request an account.

Whitepaper: Design Technology Co-Optimization of 3D-monolithic standard cells and SRAM exploiting dynamic back-bias for ultra-low-voltage operation

To download your free white paper, please fill out the form below:

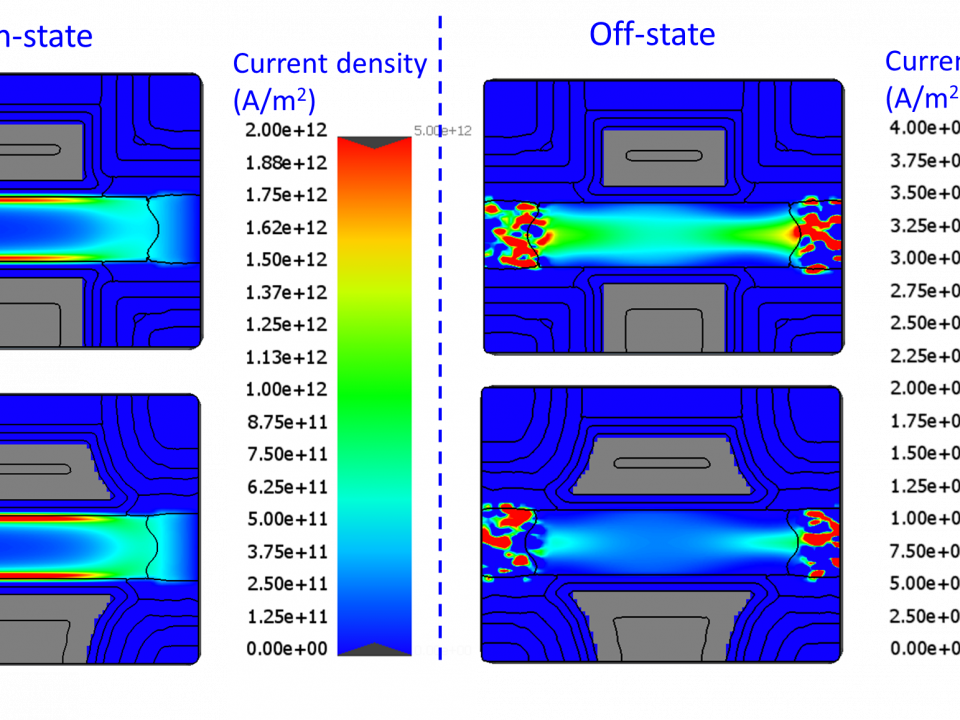

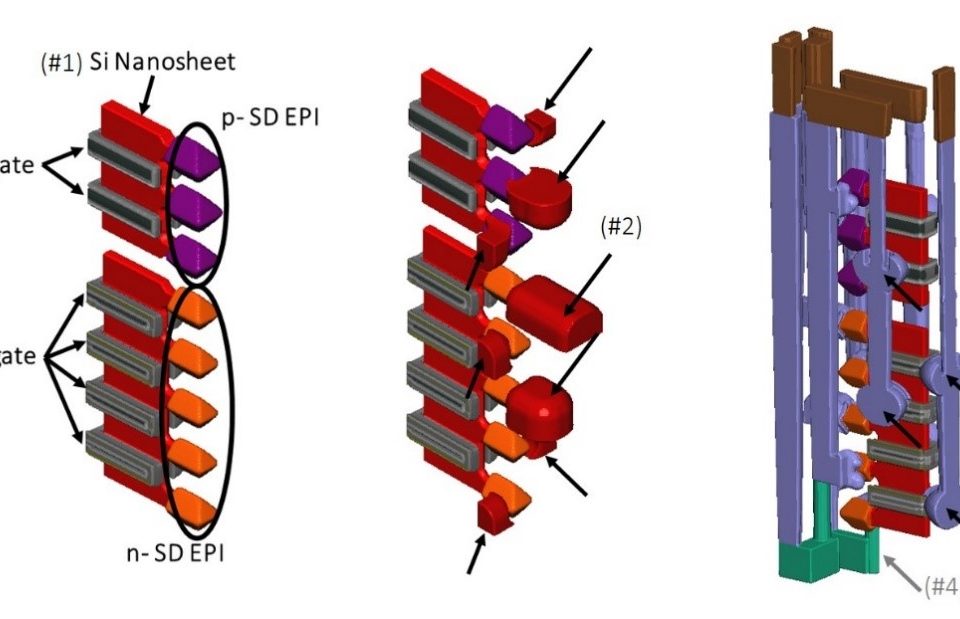

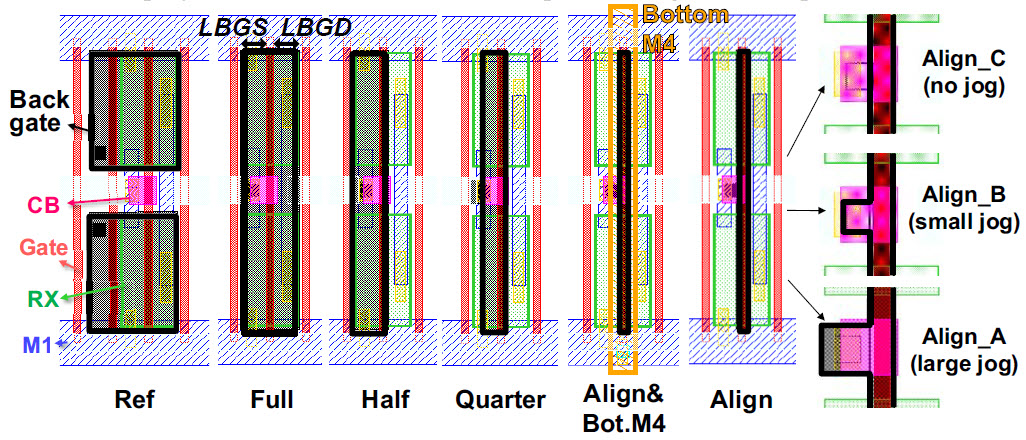

We have fabricated 3D-monolithic transistors on two tiers. We experimentally evidence the asymmetric double-gate (DG) behavior of a top-tier transistor, resulting in a better ON-state current (ION) / OFF-state current (IOFF) tradeoff than in single-gate (SG) mode. Moreover, a 3DYshared contact between a top and bottom electrode is experimentally demonstrated; paving the way for a local back gate, possibly connected with the top gate by a 3D-shared contact. Assuming such a construct, we have performed extensive layout and spice simulations of standard cells and SRAMs. We evidence that the back-gate overlap on the source and drain must be minimized to mitigate the parasitic capacitances. The best layout configurations of a loaded 1-finger inverter yields a 24% frequency gain at a given static power and VDD=0.6V supply voltage, compared to SG, or to a static power divided by 5, compared to SG under Forward Body Bias (FBB). These performance boosts may be obtained without any area penalty and assuming a 20nm-thin BOX. Similarly, a 29% improvement of the read and write currents of 6T SRAMs is contemplated at VDD=0.8V. Such new functionality provided by 3D-monolithic even enables maNing 4T SRAMs that are fully functional at VDD=0.8V by improving their retention and, in turn, the maximum number of bitcells per column from 50 (SG) to 300 with a dynamic back-bias.

© 2017 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

You might also be interested in:

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]