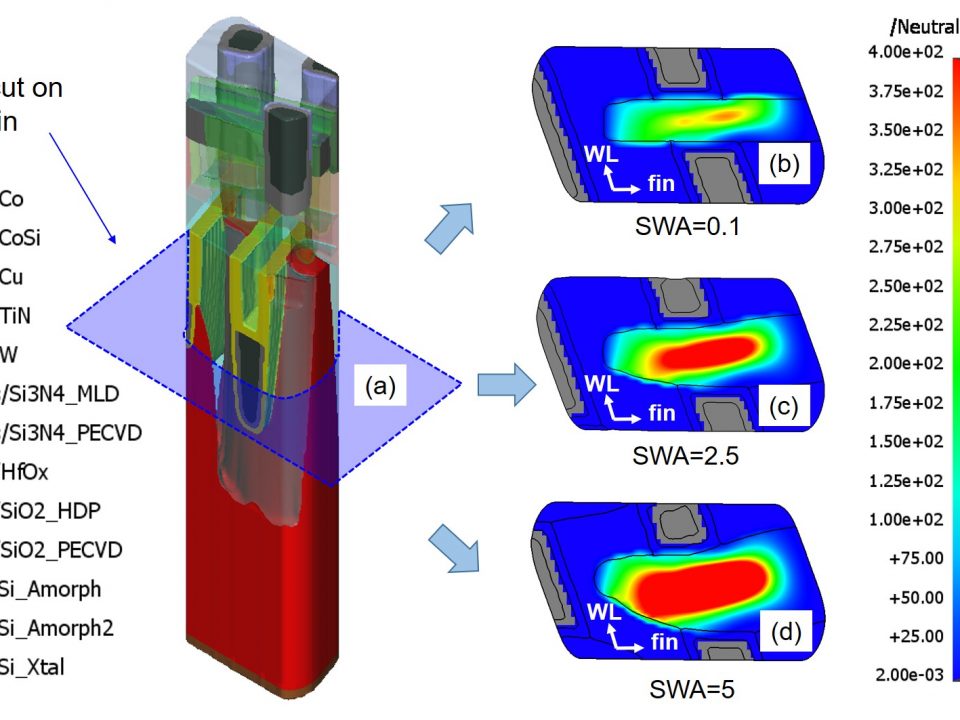

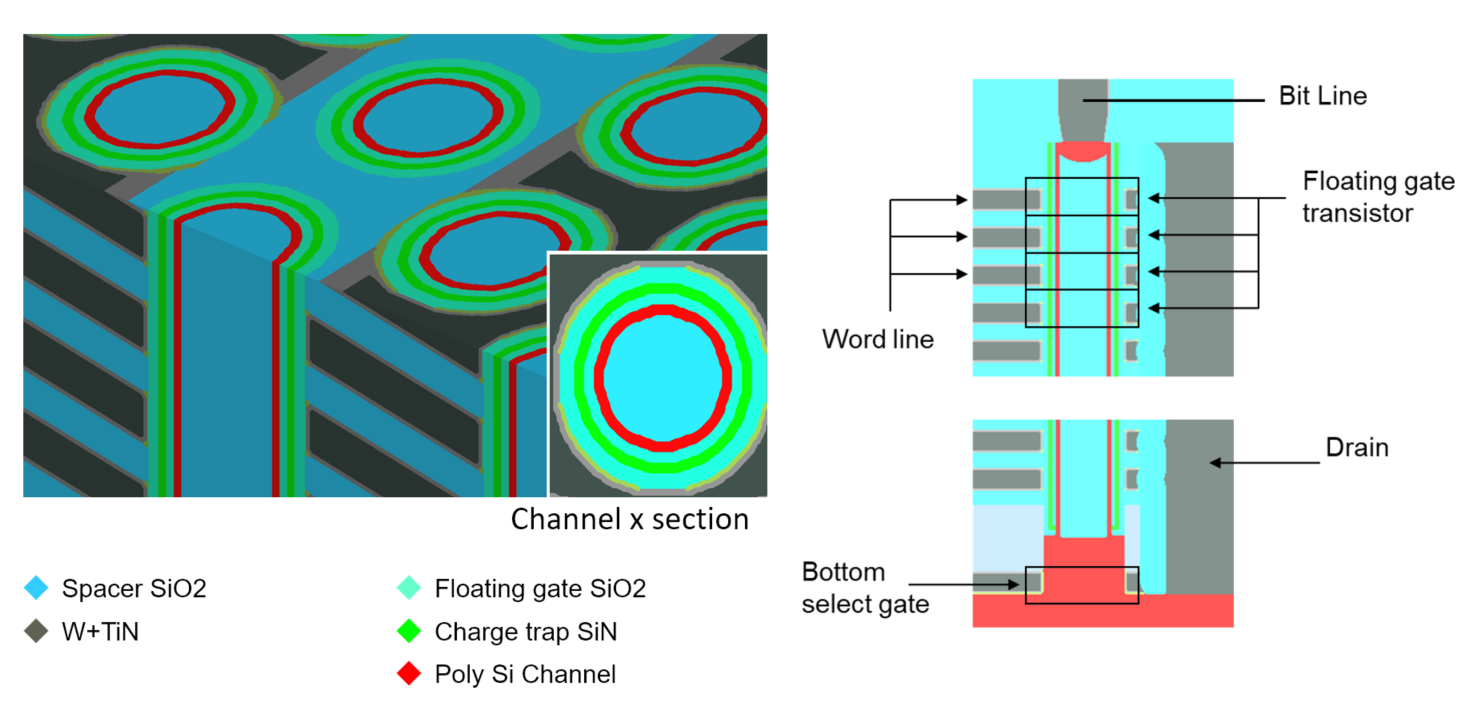

Innovative Solutions to Increase 3D NAND Flash Memory Density

January 25, 2019

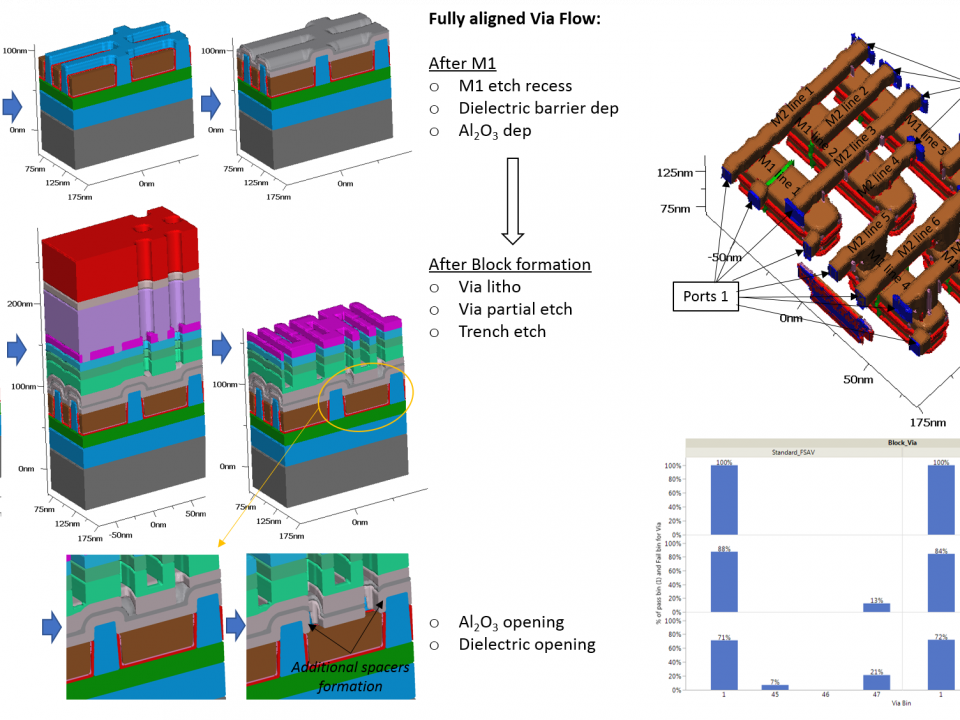

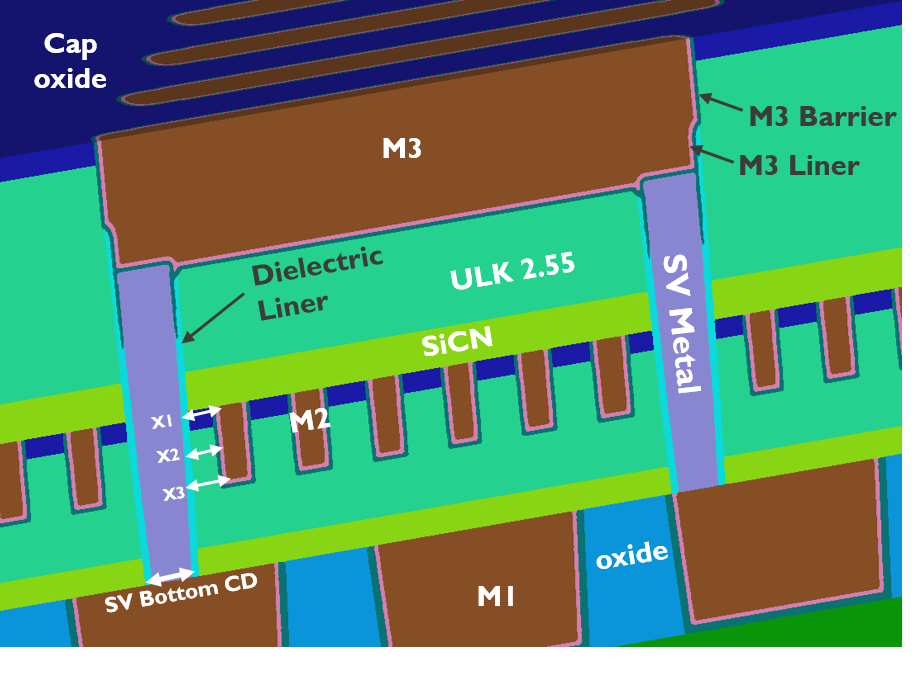

CMOS Area Scaling and the Need for High Aspect Ratio Vias

February 8, 2019You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. If you do not have an account, we invite you to request an account.

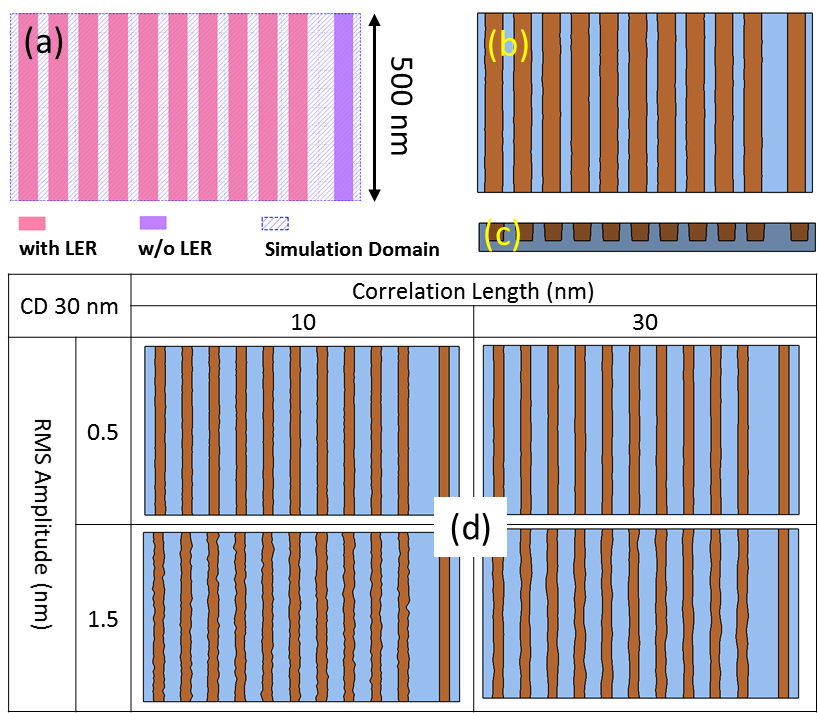

Whitepaper: Process Modeling Exploration for 8 nm Half-Pitch Interconnects

To download your free white paper, please fill out the form below:

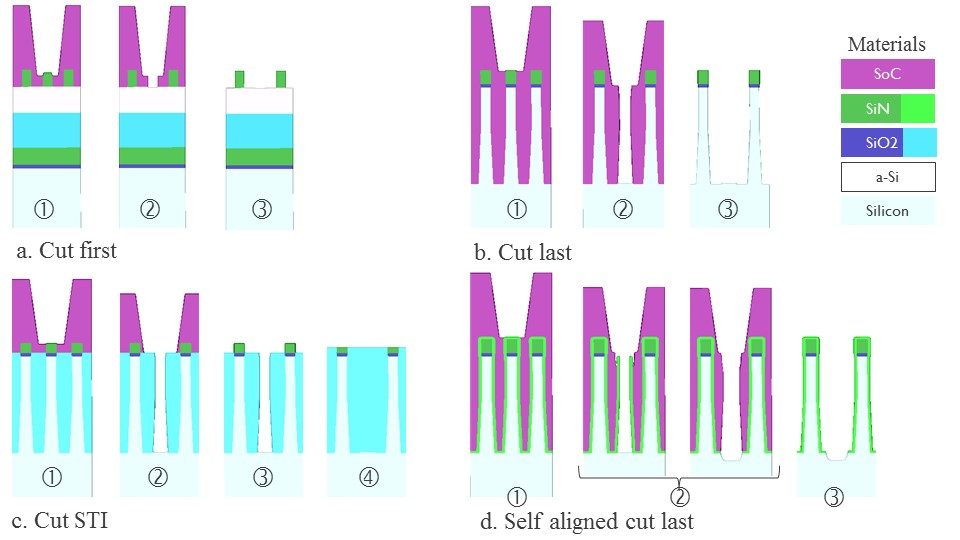

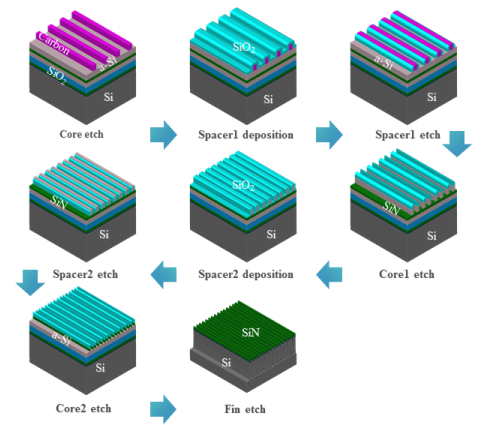

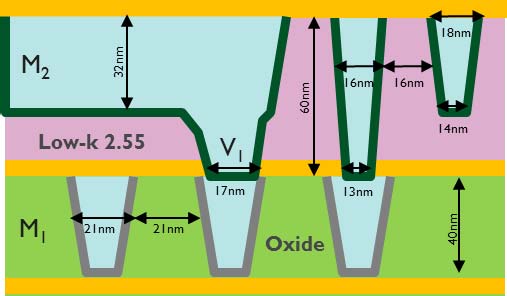

In this paper, we simulate eSADP, eSAQP and iSAOP patterning options to enable fabrication of 8 nm Half-Pitch (HP) interconnects. We investigate the impact of process variations and patterning sensitivities on pitch walking and resistance performance. The overall yield is also calculated for eight line CDs as well as M2-via-M1 via segment resistance and compared for all options. Process sensitivity simulation results enable us to evaluate the most robust options for 8 nm HP patterning.

© 2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

You might also be interested in:

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

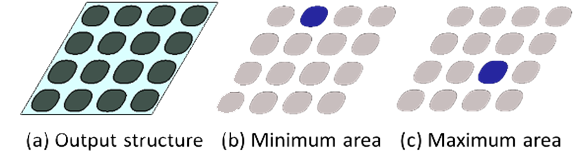

Impact of EUV Resist Thickness on Local Critical Dimension Uniformities for <30 nm CD Via Patterning

Impact of EUV Resist Thickness on Local Critical Dimension Uniformities for <30 nm CD Via Patterning

You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]