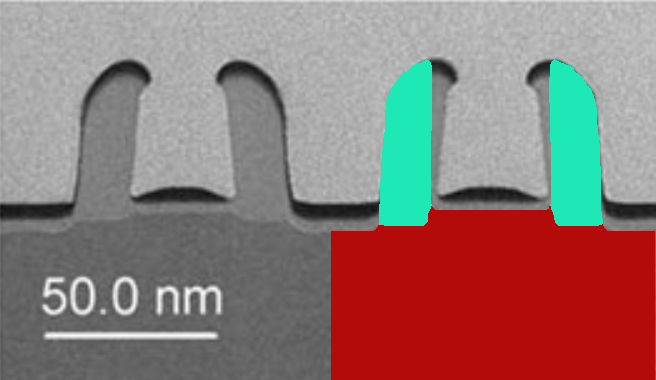

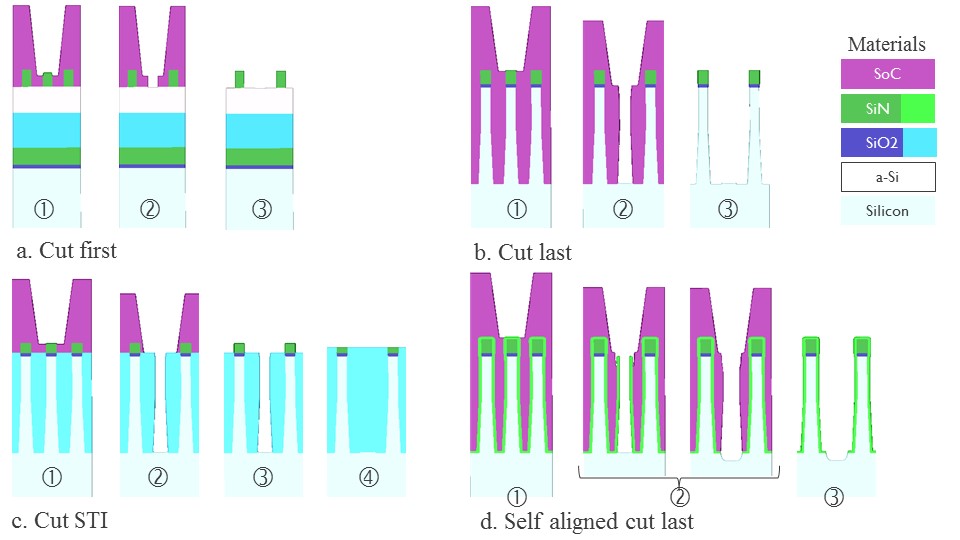

Self-aligned Fin Cut Last Patterning Scheme for Fin Arrays of 24nm Pitch and Beyond

April 11, 2019Advances in 3D CMOS Image Sensors Optical Modeling: Combining Realistic Morphologies with FDTD

September 9, 2019You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. If you do not have an account, we invite you to request an account.

Whitepaper: Backside Power Delivery as a Scaling Knob for Future Systems

To download your free white paper, please fill out the form below:

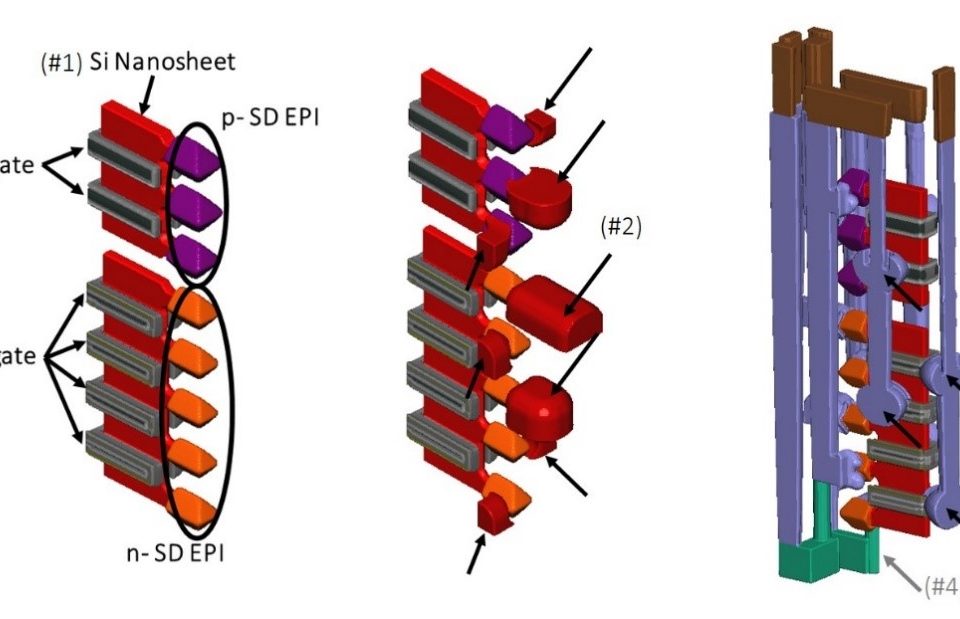

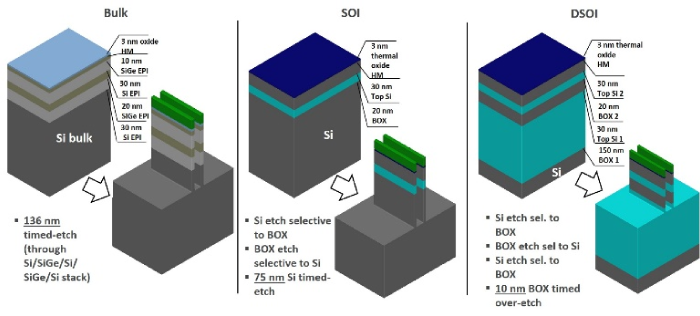

Standard cell track height scaling provides us with sufficient area scaling at the standard cell library level. The efficiency of this technique and the complexities involved with this scaling method have been discussed in detail [1,2]. However, the area benefits of standard cell track height scaling diminish when we consider the complexities of incorporating on-chip power grid into the DTCO exploration loop. We have previously outlined several layout techniques to improve the utilization density of this scaling technology [2,4]. However, the proposed techniques only minimize the impact of the power grid on the design. In this work, we discuss the need to combine 3D – μTSV technology and logic technology to decouple the power grid from the design budget. The proposed technique delivers power from the backside of a thinned device wafer using the process steps depicted in Figure 4. Our analysis demonstrates significant area savings and IR-drop reduction. We use SPICE simulations to extract grid resistances as part of our technology targeting process, based upon a high-level on-chip PDN model. We also verify our findings using a commercially available EDA toolchain.

© (2019) COPYRIGHT Society of Photo-Optical Instrumentation Engineers (SPIE). Downloading of the abstract is permitted for personal use only.

Bharani Chava, Khaja Ahmad Shaik, Anne Jourdain, Sofiane Guissi, Pieter Weckx, Julien Ryckaert, Geert Van Der Plaas, Alessio Spessot, Eric Beyne, and Anda Mocuta "Backside power delivery as a scaling knob for future systems", Proc. SPIE 10962, Design-Process-Technology Co-optimization for Manufacturability XIII, 1096205 (20 March 2019);

https://doi.org/10.1117/12.2514942

You might also be interested in:

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]