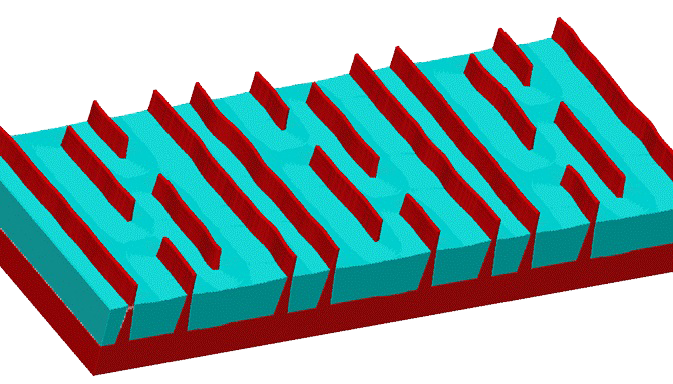

Back-End-of-Line (BEOL) Metallization

August 28, 2013

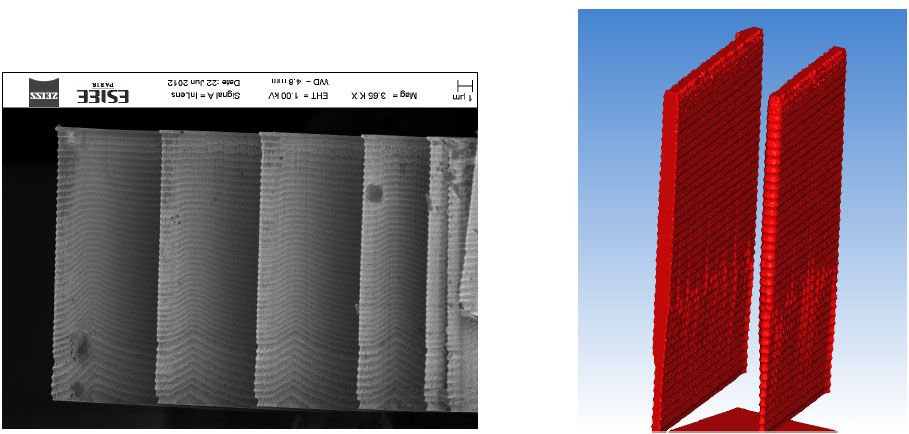

Evaluating MEMS Device Virtual Metrology & DRIE

March 18, 2014You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. If you do not have an account, we invite you to request an account.

Whitepaper: 22nm Technology Yield Optimization Using Multivariate 3D Virtual Fabrication

To download your free white paper, please fill out the form below:

IBM, Coventor present 22nm Virtual Fabrication Success at SISPAD

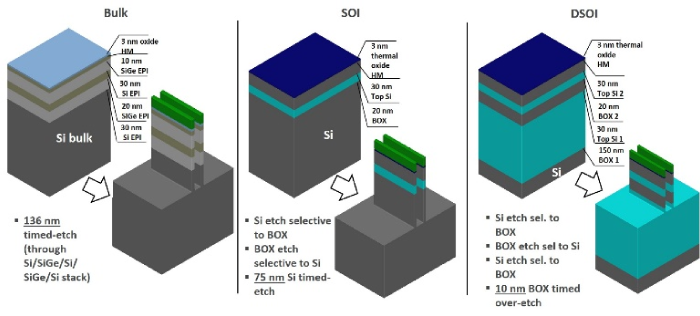

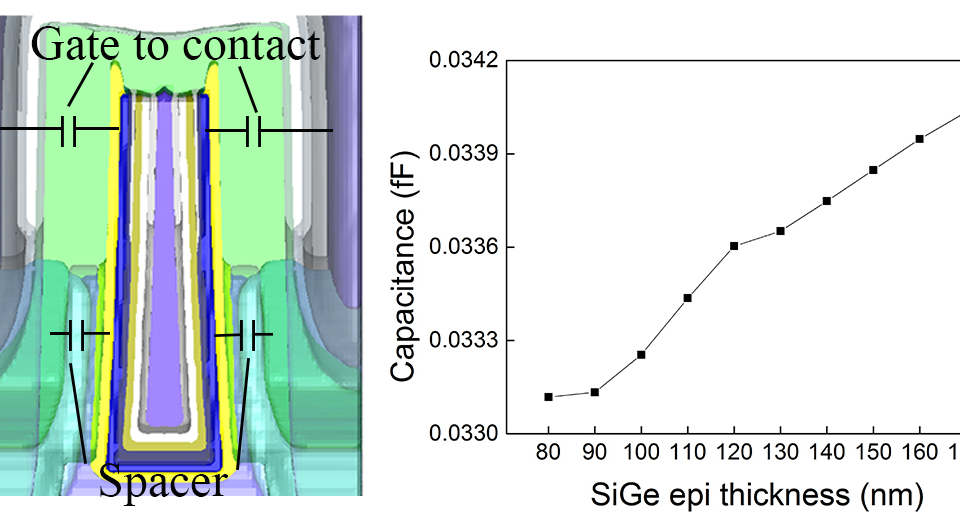

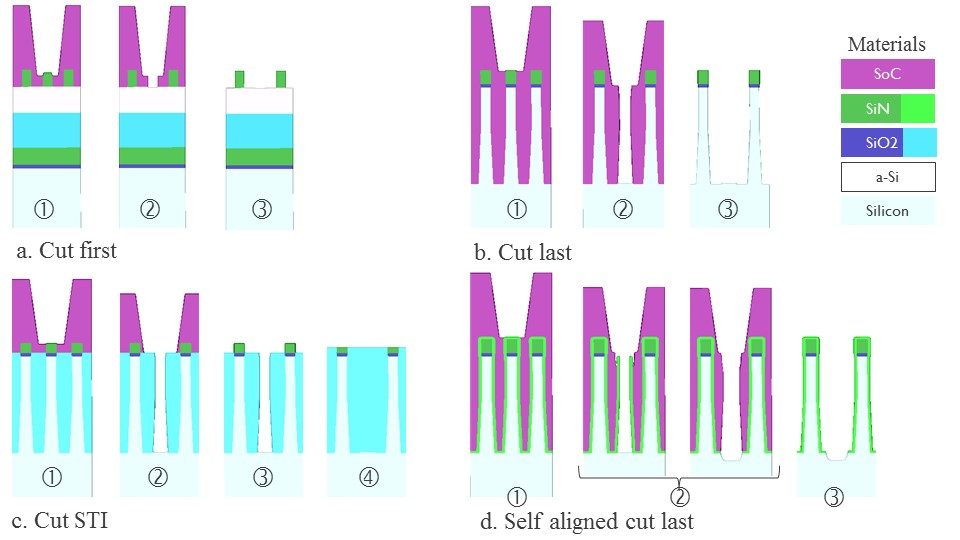

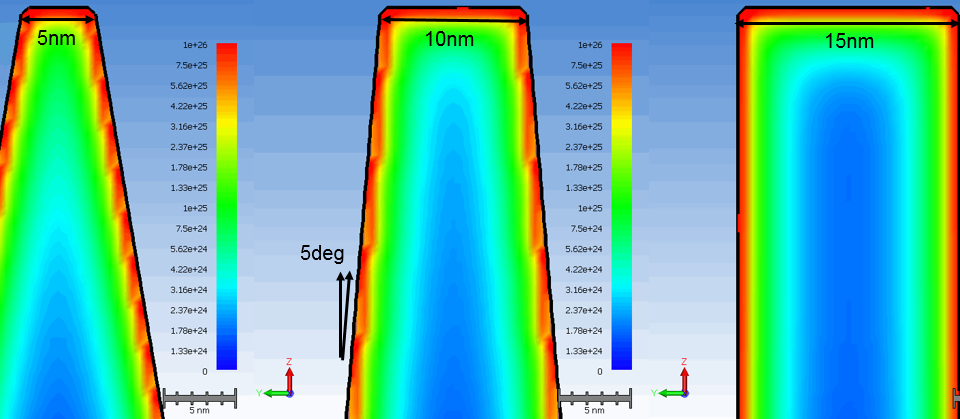

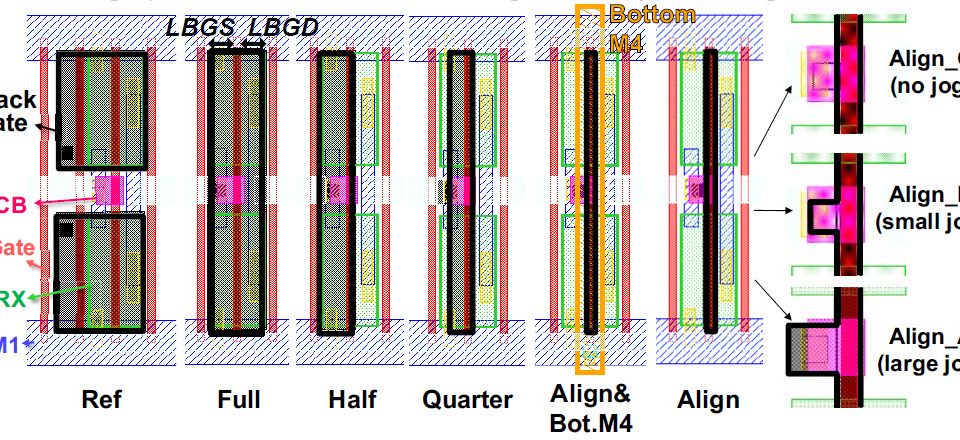

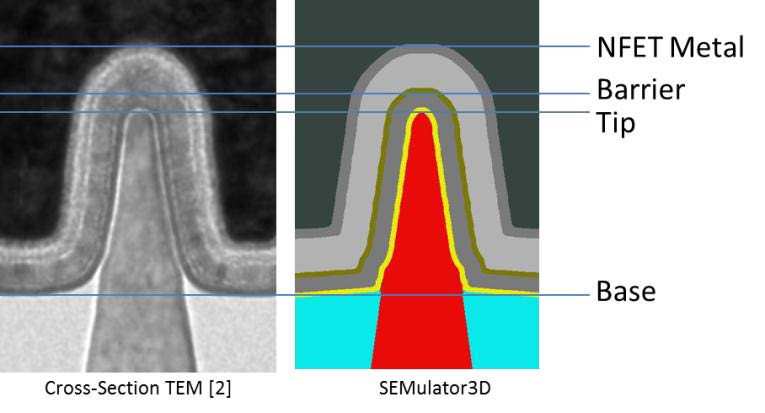

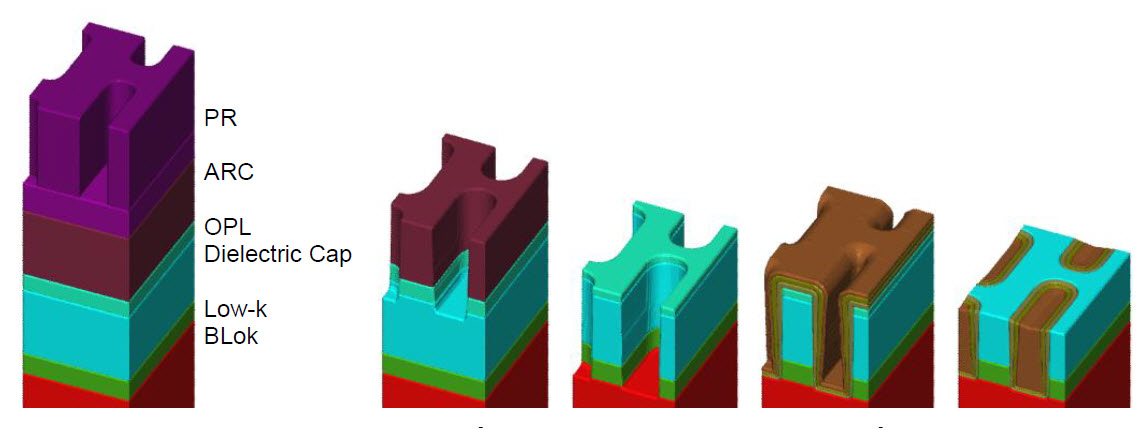

This paper, jointly presented by IBM and Coventor at the 2013 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD) presents a technology development methodology that relies on 3D virtual fabrication to rapidly improve yield by increasing tolerance to multilevel process variation. This methodology has been successfully implemented in the development and yield ramp of high-performance 22nm SOI CMOS technology. Based on virtual metrology, dedicated test site structures were designed and implemented, with electrical results corroborating virtual findings, validating the methodology. This 3D virtual fabrication technique was used to implement a delicate process change, and the same test site structures validated the improved process window yield.

You might also be interested in:

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

Impact of EUV Resist Thickness on Local Critical Dimension Uniformities for <30 nm CD Via Patterning

Impact of EUV Resist Thickness on Local Critical Dimension Uniformities for <30 nm CD Via Patterning

You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]