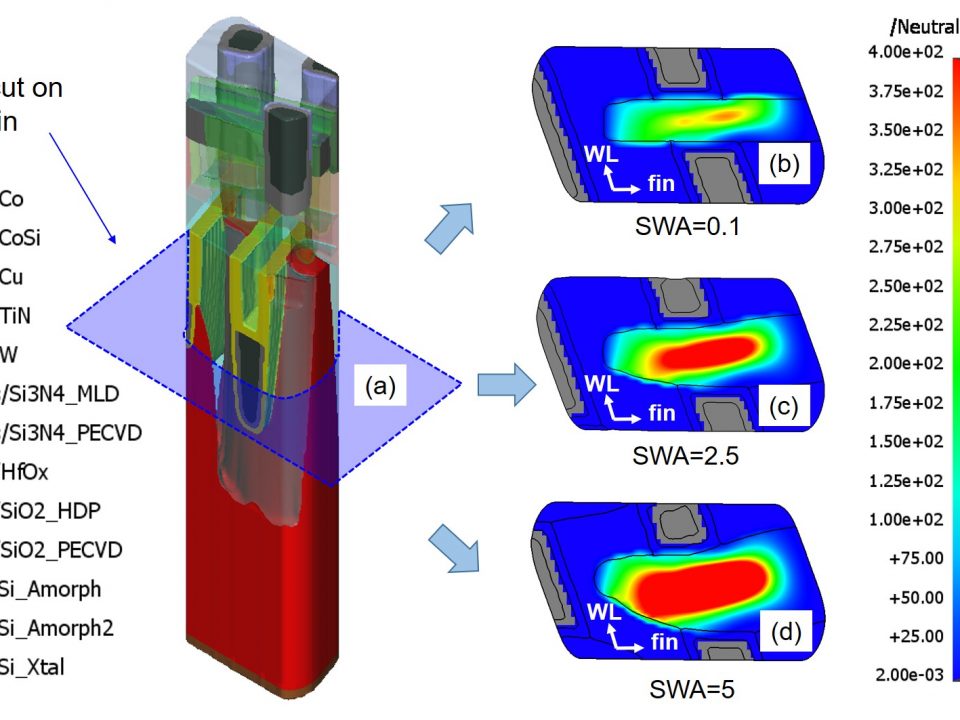

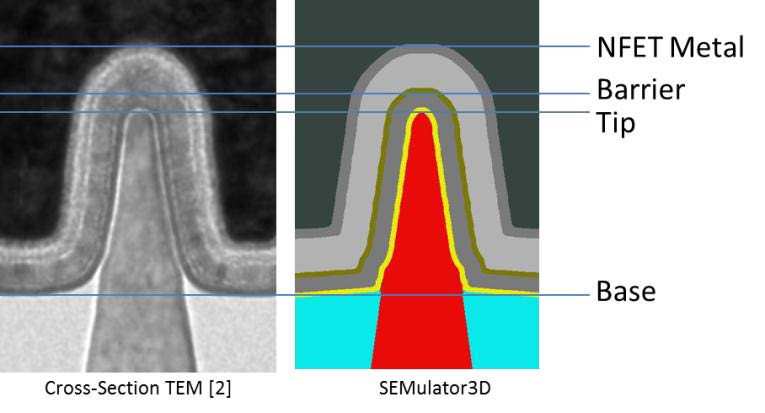

FinFET Front End of Line FEOL Process Integration

May 26, 2013

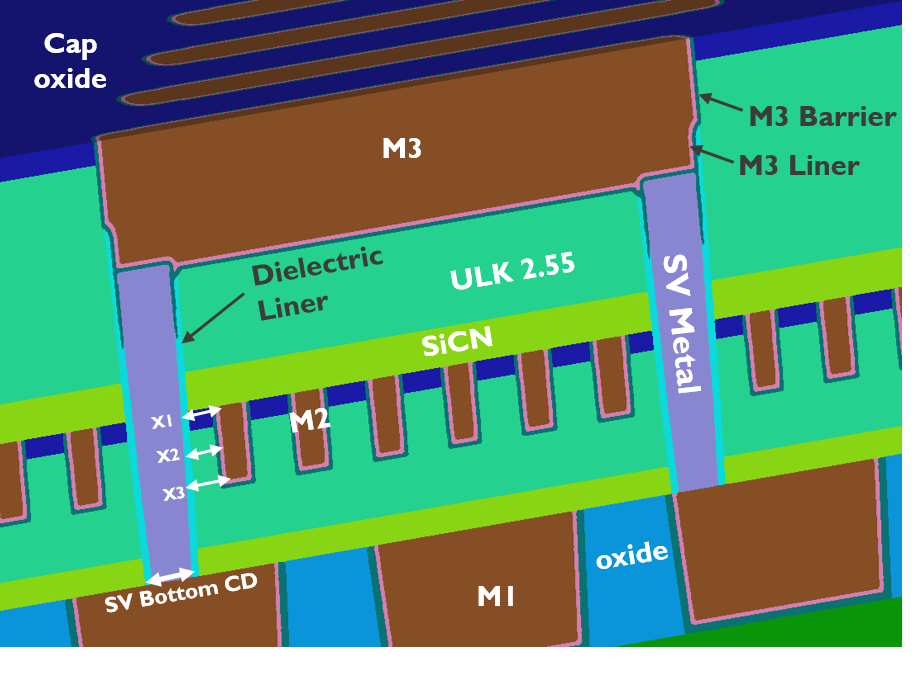

Back-End-of-Line (BEOL) Metallization

August 28, 2013You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. If you do not have an account, we invite you to request an account.

Whitepaper: Back-End-of-Line (BEOL) Virtual Patterning

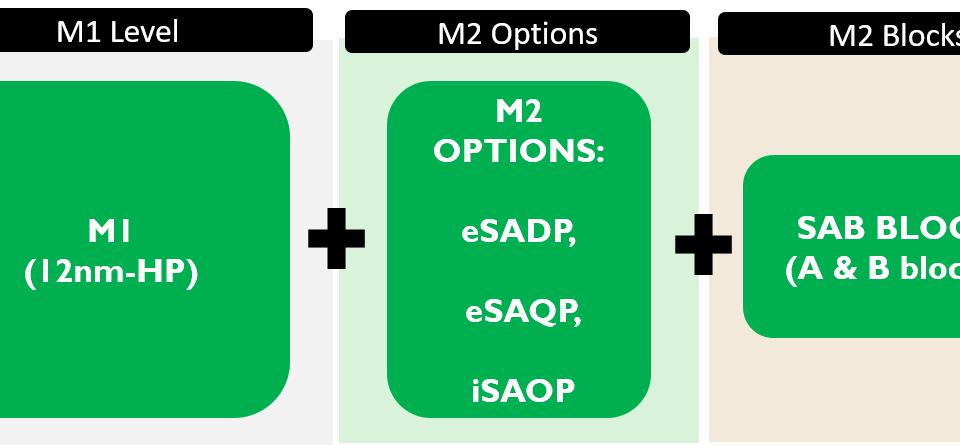

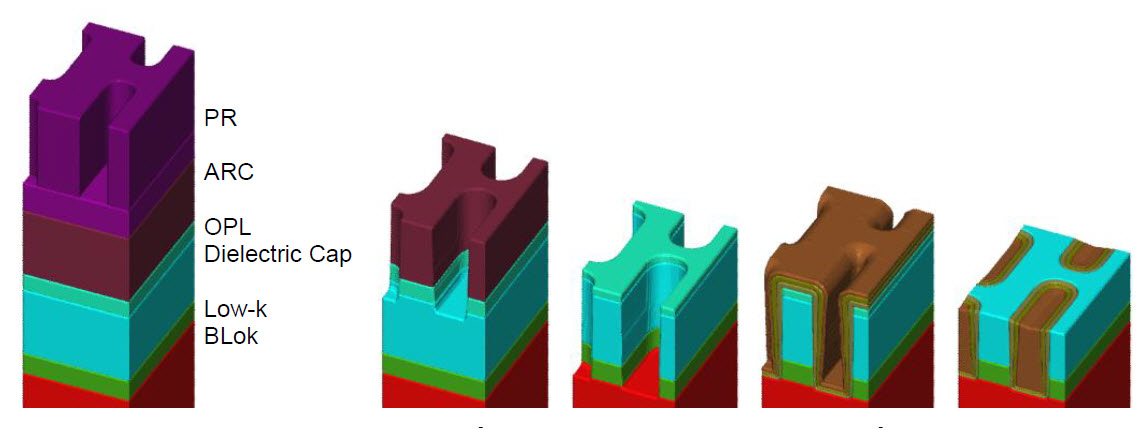

Interconnect requirements for the 22nm technology node and beyond, driven by shrinking FEOL geometry, push the limits of unit process tools for BEOL as well as FEOL. Lengthy and costly in-fab experiments are required to ensure that the integrated BEOL process meets local performance and cross-wafer uniformity requirements. Virtual fabrication experiments conducted with SEMulator3D can reduce the amount of in-fab experimentation. This white paper uses a hypothetical M2-V1-M1 module fabricated with a Trench First Metal Hard Mask with Self-Aligned Vias (TFMHM-SAV) integration approach to demonstrate the benefits of virtual fabrication.

You might also be interested in:

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

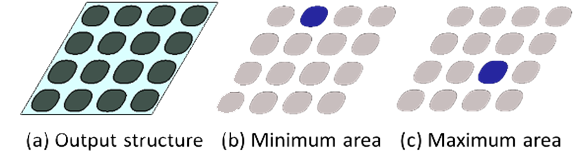

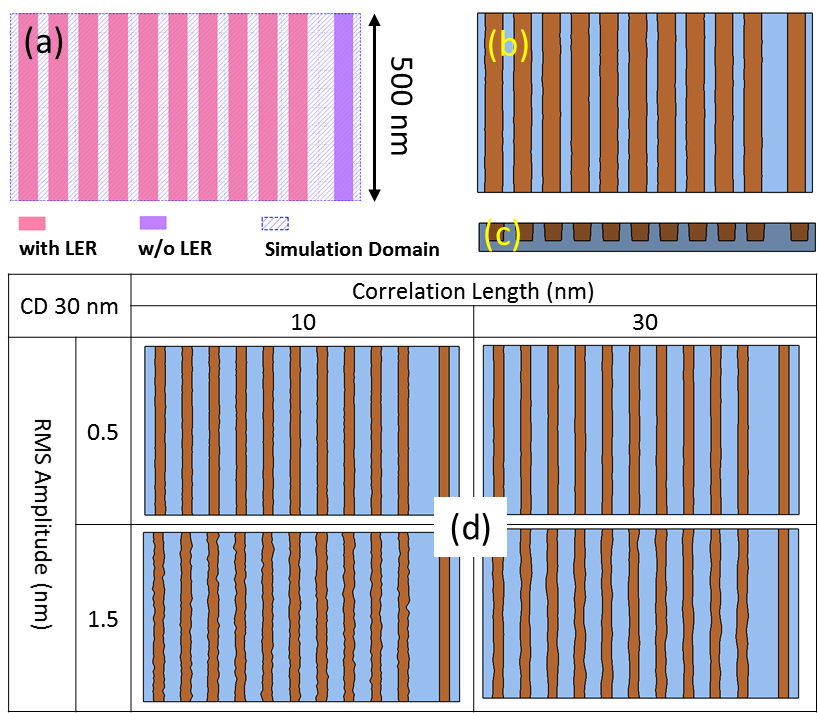

Impact of EUV Resist Thickness on Local Critical Dimension Uniformities for <30 nm CD Via Patterning

Impact of EUV Resist Thickness on Local Critical Dimension Uniformities for <30 nm CD Via Patterning

You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]

- You must have an account on our Customer Portal to access this content. If you already have an account, please log in using the form below or to the right. […]